# Vedic Architecture for Math Processors

Jayesh R. Koli, Aniket Mhatre, Deepak Kumar, Vibhu Layal Department of Department of Department of Department of Electronics Engineering, Electronics Engineering, **Electronics Engineering Electronics Engineering** PIIT PIIT **PIIT** PIIT New Panvel, New Panvel New Panvel New Panvel Maharashtra, India Maharashtra, India Maharashtra, India Maharashtra India jayesh.koli16@gmail.com mhatre\_aniket@rediffmail.com deepaksharmas61@yahoo.com vibhulayal@gmail.com

Abstract typical consists of ALU processor (Arithmetic and Logic Unit) which performs all the arithmetic operations which is assigned to it, hence the computing power of the processor is totally based on it. Nowadays we are obsessed with the high end fast processors to be in are cell phones, laptops, desktops etc. So there has been race among the designers to design very high speed, and compact processor for the upcoming electronic devices. Even though the designers have succeeded in designing very high speed processors but most of them lack due to space complexity and power consumption. Thus this paper gives an ancient Indian technique known as Vedic Mathematics which is utilized to implement multiplier and divider for fast multiplication and division etc. It will give best results in terms of speed, area and power consumption.

Keywords: space complexity, latency, Vedic Mathematics, multiplier, divider.

#### I. INTRODUCTION

For any DSP processor which controls LCD has to do multiplication and division for n number of times that also in very short time in the range of nanoseconds. So there have been

many algorithms devised for multiplication and division in DSP's some of them are Wallace tree, Array multiplier, Booth's algorithm etc. Out of them Booth's algorithm is the fastest algorithm for multiplication but it has two disadvantages one is complex circuitry another is more power consumption.

#### II. OBJECTIVE

The objective of the good multiplier and divider is to provide a compact, high speed and low power consumption unit. Being an essential part of arithmetic processing unit multipliers and dividers are in extremely high demand on its speed and low power consumption. To reduce the significant power consumption the design should involve less number of operations so as to diminish the dynamic power consumption which is dominant of all. Also the design could be easily implemented using VLSI technology.

#### III. VARIOUS METHODS AND ITS PROS AND CONS

There are many ways to perform multiplication in binary system. It depends on the performance factors like latency, throughput, area, and design complexity. Some of them are explained below.

A. Array Multiplier

Array multiplier is an efficient layout of a combinational multiplier which performs the 1x1 bit multiplication.

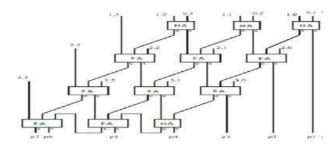

The array multiplier is as shown below.

Figure 1. Array multiplier

Array Multiplier gives more power consumption as well as optimum number of components required, but delay for this multiplier is larger. It also requires larger number of gates because of which area is also increased; due to this array multiplier is less economical. Thus, it is a fast multiplier but hardware complexity is high.

#### B. Wallace tree multiplier

A fast process for multiplication of two numbers was developed by Wallace. Using this method, a three step process is used to multiply two numbers; the bit products are formed, the bit product matrix is reduced to a two row matrix where sum of the row equals the sum of bit products, and the two resulting rows are summed with a fast adder to produce a final product. Wallace tree is a tree of carry-save adders arranged products are formed, the bit product matrix is reduced to a two row matrix where sum of the row equals the sum of bit products, and the two resulting rows are summed with a fast adder to produce a final product. Wallace tree is a tree of carry-save adders arranged as shown in figure 2

Figure 2. Wallace tree multiplier

A carry save adder consists of full adders like the more familiar ripple adders, but the carry output from each bit is brought out to form second result vector rather being thanwired to the next most significant bit. The carry vector is 'saved' to be combined with the sum later. In the Wallace tree method, the circuit layout is not easy although the speed of the operation is high since the circuit is quite irregular.

#### C. Booth multiplier

Another improvement in the multiplier is by reducing the number of partial products generated.

The Booth recording multiplier is one such multiplier; it scans the three bits at a time to reduce the number of partial products. These three bits are: the two bit from the present pair; and a third bit from the high order bit of an adjacent lower order pair. After examining each triplet of bits, the triplets are converted by Booth logic into a set of five control signals used by the adder cells in the array to control the operations performed by the adder cells.

To speed up the multiplication Booth encoding performs several steps of multiplication at once. Booth's algorithm takes advantage of the fact that an adder subtractor is nearly as fast and small as a simple adder.

The method Booth recording reduces the numbers of adders and hence the delay required to produce the partial sums by examining three bits at a time. The high performance of booth multiplier comes with the drawback of power consumption. The reason is large number of adder cells required that consumes large power.

# IV.ANCIENT INDIAN VEDIC METHOD FOR MULTIPLICATION

The idea for designing the multiplier and adder unit was adopted from ancient Indian mathematics "Vedas". Based on those formulae, the partial products and sums are generated in single step which reduces the carry propagation from LSB to MSB. The implementation of the Vedic mathematics and their application to the complex multiplier ensured substantial reduction of propagation delay in comparison with Distributed Array (DA) based architecture and parallel adder based implementation which are most commonly used architectures.

Reduced bit multiplication algorithm for digital arithmetic is shown. It mainly consisted of the in depth explanation of Urdhva tiryakbhyam sutra and the Nikhilam sutra. These sutras are the extracts from the Vedas which are the store house of knowledge. The former is suggested for smaller numbers and the latter is suggested for larger numbers.

#### A. Urdhva-Tiryagbhyam Sutra

Urdhva-tiryagbhyam sutra is the general formula applicable to all cases of multiplication and also very useful in the division of a large number by another large number.

The formula itself is very short and terse, consisting of only one compound word and means "vertically and cross-wise". It results in the generation of all partial products along with the concurrent addition of these partial products in parallel. Since there is a parallel generation of the partial products and their sums, the processor becomes independent of the clock frequency. The advantage here is that parallelism reduces the

need of processors to operate at increasingly high clock frequencies. A higher clock frequency will result in increased processing power, and its demerit is that it will lead to increased power dissipation resulting in higher device operating temperatures.

By employing the Vedic multiplier, all the demerits associated with the increase in power dissipation can be negotiated. Since it is quite faster and efficient its layout has a quite regular structure. Owing to its regular structure, its layout can be done easily on a silicon chip. The Vedic multiplier has the advantage that as the number of bits increases, gate delay and area increases very slowly as compared to other multipliers, thereby making it time, space and power efficient. It is demonstrated that this architecture is quite efficient in terms of silicon area/speed.

The illustration of this method is considered with the multiplication of two decimal numbers 123 and 135

By western method

123

X <u>135</u>

615

3690

12300

16605

By urdhva-tiryakbhyam sutra:

- 1. We multiply the left-hand-most digits vertically to obtain the left-hand-most part of the answer; 1x1=1

- 2. Then we multiply 1 and 3, and 1 and 2 cross-wise and add the result to get the sum 5 as the second part of the answer.

- 3. Then we multiply cross-wise 1 and 5, and 1 and 3 and, vertically 2 and 3 and add the result to get the sum 14 as the third part of the answer.

- 4. Then multiply 2 and 5, and 3 and 3 crosswise and add the

result to get the sum 14 as the fourth part of the answer.

5. Then multiply right-hand-most digits 3 and 5 to get the result 15 as the last part of the answer. The partial products so obtained is written as shown below

123 135

1:5:14:19:15

998 X <u>997</u> 6986 89820 <u>898200</u> 995006

We can write the final answer as

123 135 1:5:4:9:5 0:1:1:1:0 1 6 6 0 5

This method is very useful when the numbers are small to moderate but what happens if the numbers are very large, for that purpose the Vedic math has given another technique which is efficient for multiplication of large numbers it is *Nikhilam Sutra*.

#### B. Nikhilam Sutra

The sutra reads Nikhilam Navatascaramam Dasatah which, literally translated, means: "all from 9 and last from 10". Suppose we have to multiply two large numbers 998 and 997.

By western method:

998 X <u>997</u>

> 6986 89820

898200

995006

By nikhilam sutra:

- 1. We first select our base for the calculation which is the power of 10 and nearest to the numbers to be multiplied.

- 2. In this case the base is 1000 and we calculate the deficiency of each number from 1000.

- 3. For 998 it is 002 while for 997 it is 003

- 4. Then we append negative sign as the numbers are less than 1000.

998 -002 997 -003

- 5. Now we can write the right-most-part of the answer by multiplication of the deficits which is -002x-003=006.

- 6. To obtain the left-most-part of the answer we subtract 003 from 998 or subtract 002 from 997 to get the result as 995.

- 7. Thus we can write the final answer as shown below.

998 -002 997 -003 995 /006

Hence we conclude that urdhva tiryakbhyam gives best result for the small numbers while nikhilam sutra is good at large numbers. So by integrating these two modules, we can design an efficient and intelligent multiplier.

C. Proposed architecture using urdhva tiryagbhyam

If the numbers are small then multiplication with Urdhva

Tiryagbhyam is affordable and its implementation is given as follows

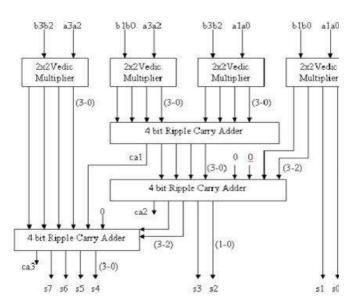

Figure 3. 4-bit urdhva tiryagbhyam multiplier

The two 4-bit no's a3a2a1a0 and b3b2b1b0 are multiplied and the product obtained is 8-bit no s7s6s5s4s3s2s1s0.

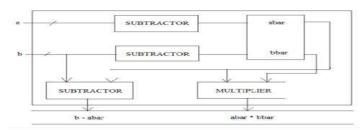

#### D. Proposed architecture using nikhilam sutram

Figure 4. 4-bit nikhilam multiplier

If the numbers a and b are large than nikhilam multiplier is best suited. In this the final product is s(7 to 4) = b - abar and s(3 to 4)0) = a bar \* b bar. By integrating these modules we obtain an efficient multiplier which has high speed, less area and low power consumption. The integrated multiplier is as follows:

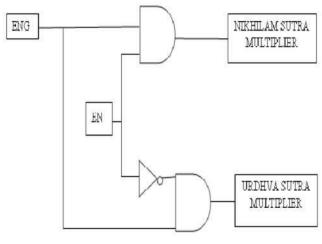

Figure 5. Proposed Integrated Vedic multiplier architecture

The concept is that, the initial conditions are set at the start (say) at around 20% from the nearest base as the Nikhilam limit. If the inputs lie inside Urdhva limit, Urdhava based multiplier will perform the multiplication and if the inputs lie inside Nikhilam limit, Nikhilam based multiplier will perform the multiplication. This is extended for all higher order cases. This proposed architecture is aimed at achieving faster results. Also, when one multiplier is 'ON', the other is

'OFF'. This accounts for low power consumption of the proposed architecture.

If the number lies within the Nikhilam limit the EN=1 and thus only Nikhilam sutra multiplier is ON and if the numbers are outside the limits Urdhva Sutra multiplier is ON with EN=0. Hence at any time only one multiplier is on and it accounts for low power consumption. This integrated architecture will prove very efficient with large numbers.

#### V. ANCIENT INDIAN VEDIC METHOD FOR DIVISION

There are number of Vedic division methods like Nikhilam Sutram, Paravartya Sutram, and Dhvajank Sutram etc.

#### A. Paravartya Sutra

We first describe here the Paravartya sutra which is special case formula and read as "Paravartya Yojayet" and which means "Transpose and apply".

Suppose we have to divide 1234 by 112

| 1 1 2 | 1        | 2 | 3         | 4  |

|-------|----------|---|-----------|----|

| -1 -2 |          | - | -         |    |

|       |          |   | -         | -2 |

|       | 1        | 1 | 0         | 2  |

|       | Quotient |   | Remainder |    |

Figure 6. division using Paravartya Sutra

- 1. The divisor 112 is written on the left then we transpose all the digits except the leftmost digit write it down below as -1 -2, this is modified 10's complement.

- 2. Put as many digits of the dividend on the right as there are digits in the modified 10's complement. It gives the remainder digits while right digits give the quotient.

- 3. Then directly write down the first digit as it is.

- 4. Then multiplying 1 by the 10's complement, we get  $1 \times -1$  -

- 2 = -1 -3. Put -1 below the second digit and -

- 3 below the third digit of the dividend.

- 5. Now add the numbers under the second digit of the dividend it get 2 + -1 = 1. Then put this sum directly below it. Now multiply 1 with the modified 10' complement to get 1 x -1 - 2 = -1 - 2.

- 6. Put -1 below the third and -2 below the fourth digit of the dividend. Now add up the numbers under the third digit to get 3 + -2 + -1 = 0. Put it at the bottom. Now add up the numbers

under the fourth digit to get 4 + -2 = 2. Put it at the bottom.

7. Thus we get the 11 as quotient and 02 as remainder.

- 1. Here divisor is 73 and dividend is 111. So we find the 10's complement of 73 just by subtracting 73 from the nearest base which is 100 to get 100 - 73

- = 27. Put 27 just below the 73.

- 2. Next we split the dividend into a left-hand part for the quotient and right-hand part for the remainder. Put as many digits to the right as there are in the 10' complement. In this case we put two digits to the right and 1 digit to the left.

- 3. We put down the first digit as it is to get the quotient as 1.

- 4. Then multiplying 27 by the left digit of the dividend to get 27 x = 27. Then put it under the right digit group of the dividend.

- 5. Then add up the numbers under the right digit group to get 11 +27 = 38. Thus we get the remainder as 38 and written below the right group.

Even this method proves to be hectic for the intermediate numbers. But there is another sutra which is applicable for the all cases of the division. It is Dhvajank Sutra, which means "on top of the flag".

#### C. Dhvajank Sutra

Division of 338982 by 73 with Dhyajank Sutra is explained below:

- 1. Out of the divisor 73, we put down only the first digit, i.e. 7 in the divisor column it is base digit. And put the other digit, i.e. 3 "on top of the flag" as the flag digit.

- 2. Now entire division has to be done by 7. So we first divide 38 by 7 to get 5, as the quotient and 3 as the remainder. We put 5 down as the first quotient-digit and just prefix the remainder 3 up before the 9.

- 3. So we get the 39 as our intermediate dividend, to obtain gross dividend we subtract product of first quotient digit and flag digit, i.e.  $3 \times 5 = 15$ , therefore gross dividend is 39 - 15 = 24. So now divide 24 by 7 to get 3 as the quotient and 3 as the remainder.

- 4. We put 3 down as the second quotient-digit and just prefix the remainder 3 up before the 8, to get 38 as intermediate dividend. While gross dividend is obtained by subtracting the product of second quotient digit and flag digit, i.e.  $3 \times 3 = 9$ , therefore gross dividend is 38 - 9 = 29.

- 5. So we divide 29 by 7 to get 4 as the quotient and 1 as the remainder. We put down 4 as the third quotient digit and prefix the remainder 1 up before 2. To get the intermediate dividend 12 from it we subtract 4 x 3

- =12 to get 0 as the remainder.

- 6. Thus we say Q is 534 and R is 0.

- D.3 digit by 2 digit Vedic division algorithm

A2 A1 A0 by B0 B1

Steps:

- 1. First do A2 ÷ B0 to get Z1 as quotient and C1 remainder.

- 2. Call procedure ADJUST (Z1, C1, A1, B1, B0). Now take the next dividend as K = (C1\*10+A1)-(B1\*Z1).

- 3. Do K  $\div$  B0 to get Z0 as quotient and C0 as remainder.

- 4. Call procedure ADJUST (Z0, C0, A0, B1, B0). Now our required remainder, R=(C0\*10+A0)-(B1\*Z1).Hence the quotient = Z1Z0, remainder=R.

```

5. Procedure ADJUST(H, I, E, B)

{ While((I*10+E) < B*H

H=H-1; I=I+A;

```

#### VI. CONCLUSION

The Vedic Math based multiplier and divider were discussed and explained in detail. They were compared with the existing methods. We found that the proposed architecture can prove to be an efficient design for the math processors, since it has regular structure it can be implemented easily on the silicon chip using CMOS fabrication technology. Even this proposed architecture has less number of logic gates requirement and hence low power consumption with less delay and increased calculating speed. The four bit multiplier based on the Urdhva-Tiryagbhyam was designed and implemented on Xilinx ISE 9.1 using VHDL. The simulation was carried out for the same.

#### VII. REFERENCES

- [1] Jagadguru Swami Sri Bharati Krishna Tirthaji Maharaja, "Vedic Mathematics", Motilal Banarsidas,

- Varanasi, India, 1986.

[2] Douglas L. Perry, "VHDL Programming by example" Mc Graw- Hill, fourth edition.

- [3] M. Morris Mano, "Computer System Architecture", 3rd edition, Prentice-Hall, New Jersey, USA, 1993, pp. 346-34

# Justifying Routing Misbehavior in Mobile Ad Hoc Networks

Prof.. Sonali Kathare Asst Prof.(EXTC Dept.) Pillai's Institute of Information Technology New Panvel katharesonali@gmail.com

Mr. Kailas Kathare S.D.E. Bharat Sanchar Nigam Limited Fountain Mumbai kmkathare@gmail.com

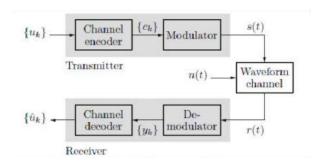

Abstract— Parallel processing and parallel computer architecture is a field with decades of experience that clearly demonstrates the critical factors of interconnect latency and bandwidth, the value of shared memory, and the need for lightweight control software. Generally, clusters are known to be weak on all these points. Bandwidths and latencies both could differ by two orders of magnitude (or more) between tightly couple MPPs and PC clusters. The shared memory model is more closely related to how applications programmers consider their variable name space and such hardware support can provide more efficient mechanisms for such critical functions as global synchronization and automatic cache coherency. And custom node software agents can consume much less memory and respond far more quickly than full-scale standalone operating systems usually found on PC clusters. In fact, for some application classes these differences make clusters unsuitable. But experience over the last few years has shown that the space and requirements of applications are rich and varying. While some types of applications may be difficult to efficiently port to clusters, a much broader range of workloads can be adequately supported on such systems, perhaps with some initial effort in optimization. Where conventional application MPP codes do not work well on

clusters, new algorithmic techniques that are latency tolerant have been devised in some cases to overcome the inherent deficiencies of clusters. As a consequence, on a per node basis in many instances applications are performed at approximately the same throughput as on an MPP for a fraction of the cost. Indeed, the price- performance advantage in many cases exceeds an order of magnitude. It is this factor of ten that is driving the cluster revolution in high performance computing.

#### I. INTRODUCTION

A "commodity cluster" is a local computing system comprising of a set of independent computers and a network interconnecting them. A cluster is local in that all of its component subsystems are supervised within a single administrative domain, usually residing in a single room and managed as a single computer system. The constituent computer nodes are commercial-off-theshelf (COTS), are capable of full independent operation as is, and are of a type ordinarily employed individually for standalone mainstream workloads and applications. The nodes may incorporate a single microprocessor or multiple microprocessors in a symmetric multiprocessor (SMP) configuration. The interconnection network employs COTS local area network (LAN) or systems area network (SAN) technology that may be a hierarchy of or multiple separate network structures. A cluster

network is dedicated to the integration of the cluster compute nodes and is separate from the cluster's external (worldly) environment. A cluster may be employed in many modes including but not limited to: high capability or sustained performance on a single problem, high capacity or throughput on a job or process workload, high availability through redundancy of nodes, or high bandwidth through multiplicity of disks and disk access or I/O channels.

#### BENEFITS OF CLUSTERS

The more expensive switches permit simultaneous transactions between disjoint pairs of nodes, thus greatly increasing the potential system throughput and reducing network contention.

While local area network technology provided an incremental path to the realization of low cost commodity clusters, the opportunity for the development of networks optimized for this domain was recognized. Among the most widely used is Myrinet with its custom network control processor that provides peak bandwidth in excess of 1 Gbps at latencies on the order of 20 microseconds. While more expensive per port than Fast Ethernet, its costs are comparable to that of the recent Gigabit Ethernet (1 Gbps peak bandwidth) even as it provides superior latency characteristics. Another early system area network is SCI (scalable coherent interface) that was originally designed to support distributed shared memory. Delivering several Gbps bandwidth, SCI has found service primarily in the European community. Most recently, an industrial consortium has developed a new class of network capable of moving data between application processes without requiring the usual intervening copying of the data to the node operating systems. This "zero copy" scheme is employed by the VIA (Virtual Interface Architecture) network family yielding dramatic reductions in latency. One commercial example is cLAN which provides bandwidth on the order of a Gbps with latencies well below 10 microseconds. Finally, a new industry standard is

emerging, Infiniband, that in two years promises to reduce the latency even further approaching one microsecond while delivering peak bandwidth of the order of 10 Gbps.

### II.THE QUADRICS NETWORK: HIGH PERFORMANCE CLUSTERING TECHNOLOGY

The interconnection network and its associated software libraries are critical components for high-performance cluster computers and supercomputers, Web-server farms, and networkattached storage. Such components will greatly impact the design, architecture, and use of future systems. Key solutions in high-speed interconnects include Gigabit Ethernet, GigaNet, the Scalable Coherent Interface (SCI), Myrinet, and the Gigabyte System Network (Hippi-6400). These interconnects differ from one another in their architecture, programmability, scalability, performance, and ability to integrate into large-scale systems. While Gigabit Ethernet resides at the low end of the performance spectrum, it provides a low-cost solution. GigaNet, SCI, Myrinet, and the Gigabyte System Network provide programmability and performance by adding communication processors on the network interface cards and implementing different types of user- level Communication protocols.

#### IV. QSNET

QsNet consists of two hardware building blocks: a programmable network interface called Elan and a highbandwidth, low latency communication switch called Elite. Elite switches can be interconnected in a fat tree topology. With respect to software, QsNet provides several layers of communication libraries that trade-off between performance and ease of use. QsNet combines these hardware and software components to implement efficient and protected access to a global virtual memory via remote direct memory access (DMA) operations.

#### V. ELAN NETWORK INTERFACE

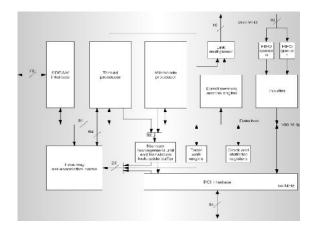

The Elan network interface (we refer to the Elan3 version of Elan in this article) connects the Quadrics network to a processing node containing one or more CPUs. In addition to generating and accepting packets to and from the network, Elan provides substantial local processing power to implement highlevel, message-passing protocols such as the Message-Passing Interface (MPI). The internal functional structure of Elan, shown in Fig. 1, centres around two primary processing engines: the microcode processor and the thread processor.

#### A. Elite switch

#### Elite provides:

Eight bidirectional links supporting two virtual channels in each direction.

An internal 16 \*8 full crossbar switch (the crossbar has two input ports for each input link to accommodate two virtual channels).

Fig. 1 Elan functional unit

- A nominal transmission bandwidth of 400 Mbytes/s in each link direction and a flow-through latency of 35 ns.

- Packet error detection and recovery with cyclicredundancy-check-protected routing and data transactions.

#### B. Packet routing

Elite networks are source routed. The Elan network interface, which resides in the network node, attaches route information to the packet header before injecting the packet into the network. The route information is a sequence of Elite link tags. As the packet moves inside the network, each Elite switch removes the first route tag from the header and forwards the packet to the next Elite switch in the route or to the final destination. The routing tag can identify either a single output link or a group of links. The Elan interface pipelines each packet transmission into the network using wormhole flow control. At the link level, the Elan interface partitions each packet into smaller 16-bit units called flow control digits or flits.10 Every packet closes with an end-of- packet token, but the source Elan normally only sends the end-of-packet token after receipt of a packet acknowledgment.

#### VI. GLOBAL VIRTUAL MEMORY

Elan can transfer information directly between the address spaces of groups of cooperating processes while maintaining hardware protection between these process groups. This capability—called virtual operation—is a sophisticated extension to the conventional virtual memory mechanism that is based on two concepts: Elan virtual memory and Elan context.

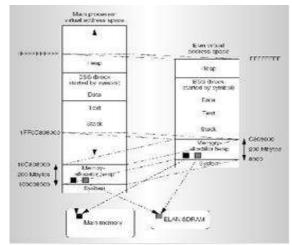

#### A.Elan virtual memory

Elan contains an MMU to translate the virtual memory addresses issued by the various on-chip functional units (thread processor, DMA engine, and so on) into physical addresses. These physical memory addresses can refer to either Elan local memory (SDRAM) or the node's main memory. To support main memory accesses, the configuration tables for the Elan MMU are synchronized with the main processor's MMU tables so that Elan can access its virtual address space. The system software is responsible for MMU table synchronization and is invisible to programmers.

The Elan MMU can translate between virtual addresses in the main processor format (for example, a 64-bit word, big-endian architecture, such as that of the Alpha Server) and virtual addresses written in the Elan format (a 32-bit word, little-endian architecture). A processor with a 32-bit architecture (for example, an Intel Pentium) requires only one-to one mapping.

#### B.Elan context

In a conventional virtual-memory system, each user process has an assigned process identification number that selects the MMU table set and, therefore, the physical address spaces accessible to the user process. QsNet extends this concept so that the user address spaces in a parallel program can intersect. Elan replaces the process identification number value with a context value. User processes can directly access an exported segment of remote memory using a context value and a virtual address

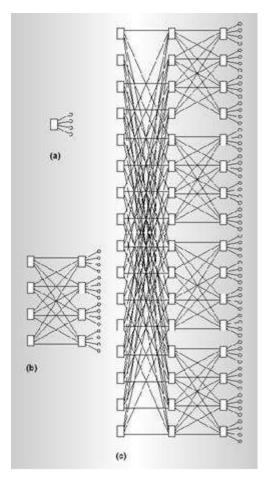

Fig. 2 Quaternary n-trees of dimensions 1(a), 2(b), 3(c)

Fig. 3

#### VII. NETWORK FAULT DETECTION AND FAULT TOLERANCE

#### A. Network fault detection and fault tolerance

OsNet implements network fault detection and tolerance in hardware. (It is important to note that this fault detection and tolerance occurs between two communicating Elans). Under normal operation, the source Elan transmits a packet (that is, route information for source routing followed by one or more transactions). When the receiver in the destination Elan receives a transaction with an ACK Now flag, it means that this transaction is the last one for the packet. The destination Elan then sends a packet acknowledgment token back to the source Elan. Only when the source Elan receives the packet acknowledgment token does it send an end-of-packet token to indicate the packet transfer's completion. The fundamental rule of Elan network operation is that for every packet sent down a link, an Elan interface returns a single packet- acknowledgment token. The network will not reuse the link until the destination Elan sends such a token.

#### B. Programming libraries

Fig. 4 shows the different programming libraries for the Elan network interface. These libraries trade off speed with machine independence and programmability. The Elan3lib provides the lowest-level, user space programming interface to the Elan3. At this level, processes in a parallel job can communicate through an abstraction of distributed, virtual, shared memory.

Fig. 4 Different programming libraries for the Elan network interface

#### VIII. ELAN3LIB LIBRARY

The Elan3lib library supports a programming environment where groups of cooperating processes can transfer data directly, while protecting process groups from each other in hardware. The communication takes place at the user level, with no copy, bypassing the operating system. The main features of Elan3lib are the memory mapping and allocation scheme (described previously), event notification, and remote DMA transfers. Events provide a general-purpose mechanism for processes to synchronize their actions. Threads running on Elan and processes running on the main processor can use this mechanism. Processes, threads, packets, and so on can access events both locally and remotely. In this way, intra-network synchronization of processes is possible, and events can indicate the end of a communication operation, such as the completion of a remote DMA. QsNet stores events in Elan memory to guarantee atomic execution of the synchronization primitives. (The current PCI bus implementations cannot guarantee atomic execution, so it is not possible to store events in main memory.) Processes can wait for an event to be triggered by blocking, busy-waiting, or polling. In addition, processes can tag an event as block copy.

Fig. 5

#### A. Elanlib and T-ports

Elanlib is a machine-independent library that integrates the main features of Elan3lib with T-ports. T-ports provide basic mechanisms for point- to-point message passing. Senders can label each message with a tag, sender identity, and message size. This information is known as the envelope. Receivers can receive their messages selectively, filtering them according to the sender's identity and/or a tag on the envelope. The T-ports layer handles communication via shared memory for processes on the same node. The T-ports programming interface is very similar to that of MPI. T-ports implement message sends (and receives) with two distinct function calls: a non-blocking send that posts and performs the message communication, and a blocking send that waits until the matching start send is completed, allowing different implementation of flavours of higher-level communication primitives. T-ports can deliver messages synchronously and asynchronously. They transfer synchronous messages from sender to receiver with no intermediate introduced by Elanlib and an implementation of MPI-2 (based on a port of MPI- CH onto Elanlib). To identify different bottlenecks, we placed the communication buffers for our unidirectional and bidirectional ping tests either in main or Elan memory. The communication alternatives between memories include main to main, Elan to Elan, Elan to main, and main to Elan.

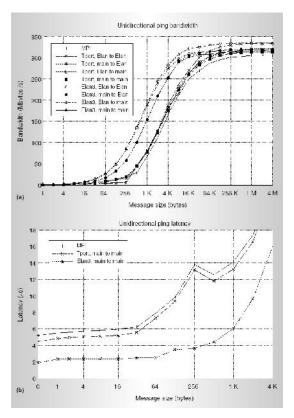

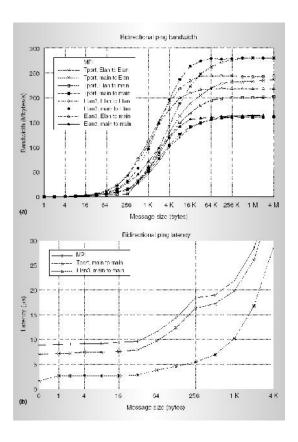

Fig. 6 Results for the unidirectional ping

#### B. Unidirectional ping

Fig. 6 shows the results for the unidirectional ping. The asymptotic bandwidth for all communication libraries and buffer mappings lies in a narrow range from 307 Mbytes/s for MPI to 335 Mbytes/s for Elan3lib. The results also show a small performance asymmetry between read and write performance on the PCI bus. With Elan3lib, the read and write bandwidth s are 321 and 317 Mbytes/s. The system reaches a peak bandwidth of 335 Mbytes/s when we place both source and destination buffers in Elan memory. We can logically organize the graphs in Fig. 6a into three groups: those relative to Elan3lib with the source buffer in Elan memory, Elan3lib with the source buffer in main memory, and T-ports and MPI. In the first group, the latency is low for small and medium sized messages. This basic latency increases in the second group because of the extra delay to cross the source PCI bus. Finally, both T-ports and MPI use the thread processor to perform tag matching, and this further increases the overhead. Fig. 6b shows the latency of messages in the range 0 to 4 Kbytes. With Elan3lib, the latency for 0-byte mess ages is only 1.9 µ s and is almost constant at 2.4 µ s for messages up to 64 bytes, because the Elan interface can pack these messages as a single write block transaction. The latency at the T-ports and MPI levels increases to 4 .4 and 5.0 μ s. At the Elan3lib level, latency is mostly at the hardware level, whereas with T-ports, system software runs as a thread in the Elan to match the message tags. This introduces the extra overhead responsible for the higher latency value. The noise at 256 bytes, shown in Fig. 6b, is due to the message transmission policy. Elan inlines messages smaller than 288 bytes together with the message envelope so that they are immediately available when a receiver requests them. It always sends larger messages synchronously, and only after the receiver has posted a matching request.

Fig. 7 shows that full network bi-directionality cannot be achieved in practice Bidirectional ping

Fig. 7 shows that full network bi-directionality cannot be achieved in practice. The maximum unidirectional value, obtained as half of the measured bidirectional traffic, is approximately 280 Mbytes/s, whereas, in the unidirectional case, it was 335 Mbytes/s. This gap in bandwidth exposes bottlenecks in the network and in the network interface. DMA engine interleaving with the in putter, the sharing of the Elan's internal data bus and link level interference in the Elite network cause this performance degradation.

#### Hotspot

A hotspot is a single memory location that processors access repeatedly. To measure QsNet's vulnerability to such hotspots, we read from and write to the same memory location from an increasing number of processors (one per SMP). Fig. 8 (next page) plots bandwidth for increasing numbers of SMPs. The upper curve of this figure shows the aggregate global bandwidth for all processes. The curves are remarkably flat, reaching 314 and 307 M bytes/s for read and write hotspots. The lower curves show the per-SMP band- Bandwidth. The scalability of this type of memory operation is very good, up to the available number of processors in our cluster.

#### IX. CONCLUSION

While there are certainly a number of differences between embedded clusters and standard clusters that have been brought out in this section, there are also a number of similarities, and in many ways, the two types of clusters are converging. Massmarket forces and the need for software portability are driving embedded clusters to use similar operating systems, tools, and inter-connects as standard clusters. As traditional clusters grow in size and complexity, there is a growing need to use denser packaging techniques and higher bandwidth, lower latency interconnects. Real- time capability is also becoming more common in traditional clusters in industrial applications, particularly as clusters become more interactive, both with people and with other hardware. Additionally, fault-tolerance is becoming more important for standard clusters: first, as they are increasingly accepted into machine rooms and subject to reliability and up-time requirements.

#### X. FUTURE WORK

As SMP become more common in clusters, we will see a natural hierarchy arise. SMP have tight coupling, and will be joined into clusters via low-latency high- bandwidth interconnection networks. Indeed, we fully expect that heterogeneous clusters of SMP will arise, having single, dual, quad, and octo-processor boxes in the same cluster. These clusters will, in turn, be joined by gigabit-speed wide-area networks, which will differ from SAN primarily in their latency characteristics. This environment will naturally have a three-level hierarchy, with each level having an order of magnitude difference in latency relative to the next layer.

This structure will have its greatest impact on scheduling, both in terms of task placement and in terms of selecting a process to run from a ready queue. Scheduling is traditionally considered an operating system activity, yet it is quite likely that at least some of this work will be carried out in middleware.

For example, as one of our research projects we are investigating thread management for mixed-mode (multithreaded and message passing) computing using OpenMP and MPI, which we believe is a natural by-product of clusters of SMP. Most cluster applications, particularly scientific computations traditionally solved via spatial decomposition, consist of multiple cooperating tasks. During the course of the computation, hot spots will arise, and a self-adapting program might wish to manage the number of active threads it has in each process. Depending on the relationship of new threads to existing threads (and their communication pattern) and the system state, a decision might be made to do one of the following:

- Add a new thread on an idle processor of the SMP where the process is already running.

- Expand the address space via distributed shared memory to include an additional node, and add a thread there.

- Add a thread to a non-idle processor already assigned to the process.

- Migrate the process to a larger SMP (e.g. from 2 nodes to 4 nodes) with an idle processor, and add a new thread there.

#### REFERENCES

[1]R.Seifert, Gigabit Ethernet: Technology and Applications for High Speed LANs, Addison Wesley, Reading, Mass., 1998.

[2]W. Vogels et al., "Tree-Saturation Control in the AC3 Velocity Cluster", Hot Interconnects vogels/clusters/ac3/hoti\_files/frame.htm (current Dec. 2001).

[3]H. Hellwagner, "The SCI Standard and Applications of SCI," SCI: Scalable Coherent Interface, Lecture Notes in Computer Science, vol. 1291, H. Hellwagner and A. Reinfeld, eds., Springer-Verlag, Heidelberg, Germany, 1999, pp. 95-116.

[4]N.J. Boden et al., "Myrinet: A Gigabit-per- Second Local Area Network, "IEEE Micro, vol. 15, no. 1, Jan. 1995, pp. 29-36.

# Automated Design of Robust PID Controller Using Genetic Algorithm

Patel Iftekar Department of Electronics Engineering PIIT, New Panvel. iftekarpatel@gmail.com

Prof.Monika Bhagwat Department of Electronics Engineering PIIT, New Panvel. monikabhagwat@yahoo.com

Prof. Ujwal Harode Department of Electronics Engineering PIIT, New Panvel. ujwal.harode@gmail.com

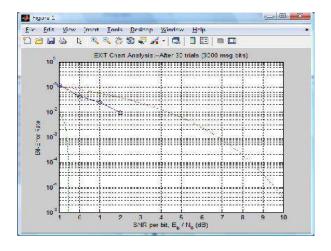

Abstract—the paper deals with the design of robust controller for uncertain SISO systems using Quantitative Feedback Theory (OFT) and optimization of controller being done with the help of Genetic Algorithm (GA). Quantitative Feedback Theory (QFT) technique is a robust control design based on frequency domain methodology. It is useful for practical design of feedback system in ensuring plant's stability by reducing the sensitivity to parameter variation and attenuates the effect of disturbances. Parameter variation or physical changes to the plant is taken into account in the QFT controller's design.

Quantitative Feedback Theory (QFT) can provide robust control for the plant with large uncertainties. The manual design with the help of QFT toolbox in Matlab is complicated and even unsolvable. The existing automatic design methods are limited in optimization. Based on the genetic algorithm (GA), a more effective automatic design methodology of QFT robust controller is proposed. Some new optimization indexes like IAE, ISE, ITAE and MSE are adopted, so the design method is more mature. To obtain good performance of the controller in a relatively short time, the manual design and the automatic design are combined. Compared with the results from the manual design method, the performance of the QFT controller based on genetic algorithms is better and the efficiency of searching scheme is the best. An illustrative example which compares manual loop shaping with automatic loop shaping is given.

Keywords—Robust controller. **Ouantitative** Feedback Theory (QFT), Genetic Algorithm(GA), Uncertainties, stability, Manual loop shaping, Automatic loop shaping, Optimization index, Matlab, Mean of the Squared Error (MSE), Integral of Time multiplied by Absolute Error (ITAE), Integral of Absolute Magnitude of the Error (IAE), Integral of the Squared Error (ISE).

#### **I.INTRODUCTION**

There are two general control systems. (i) Conventional control, and (ii) Robust control, which typically involves worst case design approach for family of plants using a single fixed controller [1]. If the design performs well for substantial variations in the dynamics of the plant from the design values, then the design is robust. Robust control deals explicitly with uncertainty in its approach to controller design. Controllers designed using robust control methods tend to be able to cope with small differences between the true system and the nominal model used for design. Quantitative Feedback Theory (QFT) is robust control method which deals with the effects of uncertainty systematically. QFT is a graphical loop shaping procedure used for the control design of either SISO (Single Input Single Output) or MIMO (Multiple Input Multiple Output) uncertain systems including the nonlinear and time varying cases. QFT, developed by Isaac Horowitz is a frequency domain technique utilizing the Nichols chart (NC) in order to achieve a desired robust design over a specified region of plant uncertainty. In comparison to other robust control methods, QFT offers a number of advantages. For the purpose of QFT, the feedback system is normally described by the two-degrees- of freedom structure. [3]

A proportional-integral-derivative controller (PID Controller) is a generic control loop feedback mechanism widely used in industrial control systems. PID controllers have dominated the process control industry over the decades owing to its associated simplicity and easiness in implementation. design of PID controllers, tuning involves selecting the amounts of Proportional, Integral and Derivative components required at the output of the controller. Since the design of PID controllers involves obtaining the P, I and D components there always occurs a compromise in the design. The design of the optimum values for the PID controller parameters has always been challenging. Many new tuning techniques have been developed for the design of PID controllers, however then still exists a scope for better tuning method. Various control strategies are used for design of control system depending on plant model. [4]

One of the most frequently used on-line tuning methods is the Genetic Algorithm (GA). The genetic algorithm is very effective at finding optimal solutions to a variety of problems. This innovative technique performs especially well when solving complex problems because it doesn't impose many limitations of traditional techniques. Due to its evolutionary nature, a GA will search for solutions without regard to the specific inner working of the problem. This ability lets the same general purpose GA routine perform well on large, complex scheduling problems. There is now considerable evidence that genetic algorithms are useful for global function optimization.

#### II.LITERATURE REVIEW

Quantitative Feedback Theory (QFT) has been applied in many engineering systems successfully since it was develop

In [7], Qingwei Wang, Zhenghua Liu, Lianjie Er presented automatic design method of QFT controller based on GA and proposed several initial optimization indexes to make the controller more practical. They proved that GA based automatic design method of QFT controller is very effective and optimization method can achieve both high performance and increased efficiency.

In [8], A Zolotas and G.D Halikias proposed an optimization algorithm for designing PID controllers, which minimizes the asymptotic open-loop gain of a system, subject to appropriate robust stability and performance QFT constraints. The algorithm is simple and can be used to automate the loopshaping step of the QFT design procedure. The effectiveness of the method is illustrated with an example.

In [6], Wenhua Chen and Donald J. Balance addressed design of robust controllers for uncertain and non-minimum phase and unstable plant using QFT technique. Benchmark examples were used to illustrate the improved method

In [11], Mario Garcia-Saenz In the first part of the paper summarized the main concepts of the Quantitative Feedback Theory (QFT) and presented a wide set of references related to the principal areas of research. In the second part of the paper introduced a method to design non-diagonal QFT controllers for MIMO systems. Finally the paper ends presenting some realworld applications of the technique, carried out by the author: an industrial SCARA robot manipulator, a wastewater treatment plant of 5000 m3/hour, a variable speed pitch controlled multipolar wind turbine of 1.65 MW and an industrial furnace of 40 meters and 1 MW.

In [10], O. Yana and M. Mazurka examined an analyticallybased algorithm for finding low order controllers that satisfy closed loop gain and phase margin constraints and a bound on the sensitivity.

In [14], K. Krishna Kumar and D. E. Goldberg proposed an approach which improves the quality and speed of manual loop shaping; Genetic Algorithm was used to provide global optimization.

In [16], P.S.V.NATRAJ Proposed an algorithm for generating QFT bounds to achieve robust tracking specifications. The proposed algorithm can generate tracking bounds over intervals of controller phase values, as opposed to discrete controller phase values in existing algorithms.

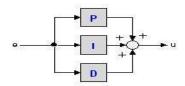

#### BASICS OF PID CONTROL SYSTEM

PID controller consists of the three terms: proportional (P) integral (I), and derivative (D). Its behavior can be roughly interpreted as the sum of the three term actions The P term gives a rapid control response and a possible steady state error, the I term eliminates the steady state error and the D term improves the behavior of the control system during transients.[4]

The Transfer function of PID controller is given b Where Kp = Gain of the system.

Ti =Integral time constant.

Td = Derivative time constant

Fig. 1 parallel form of PID

#### **III.QFT BASIC CONCEPTS**

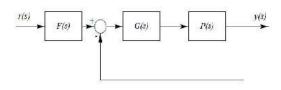

QFT is a very powerful control system design method when the Plant parameters vary over a broad range of operating conditions. The basic concept of QFT is to define and take into account, along the control design process, the quantitative Relation between the amount of uncertainty to deal with and the amount of control effort to use. The Quantitative Feedback Theory (QFT) method offers, frequency-domain based design approach for tackling feedback control problems with robust performance objectives.[3] In this approach, the plant Dynamics may be described by frequency response data, or by a transfer function with mixed (parametric and nonparametric) Uncertainty models. The basic idea in QFT is to convert design specifications at closed loop and plant uncertainties into robust stability and performance bounds on open loop transmission of nominal system and then design controller by using loop shaping [5]. The two-degree-freedom feedback system configuration of QFT is given in Fig.1.

Fig. 2 QFT Configuration, where G(s) - Controller, F(s) - pre-filter, P(s) - uncertain plant which belongs to a given plant family P.

#### IV.CONTROLLER DESIGN PROCEDURE USING QFT

Design Steps for PID Controller are as follows:

- Translation of TDS to FDS (Time Domain Specification to Frequency Domain Specification).

- 2. Generation of the Plant Set.

- 3. Generation of the Template.

- Grouping of Bounds. 4.

- 5. Intersections of Bounds.

- Loop shaping (Design of a Controller).

- Pre-filter Designs.

#### V.DESIGN EXAMPLE

A Benchmark example from OFT toolbox is considered in order to explain the various design steps OFT controller.

Consider a plant with parametric uncertainty given by:

$$P(s) = k \in [1, 10], a \in [1, 10]$$

The stability index is given by:

$$\frac{PG}{1+PG}(j\omega) \stackrel{>}{\leq} 1.2$$

And upper and lower boundaries of tracking index are,

$$TU(\omega) \le \frac{\mathbb{P}G}{1+\mathbb{P}G}(J\omega)$$

$\le TL(\omega)$

Where TU (

$$\omega$$

) =

$$\frac{\left| \frac{0.6854(j\omega+30)}{(j\omega)^2+4(j\omega)+19.752} \right| }{(j\omega)^2+4(j\omega)+19.752}$$

and TL (

$$\omega$$

) =  $(j\omega)^2 + 17(j\omega)^2 + 928(j\omega) + 120$

And output disturbance rejection bound is given by

$$\frac{|Y|}{|I|}(J\omega) \le \left| 0.02 \frac{(J\omega)^8 + 64(J\omega)^2 + 748(J\omega) + 2400}{(J\omega)^2 + 14.4(J\omega) + 169} \right|$$

Translation from TDS to FDS (Time Domain Specification to Frequency Domain Specification)

Since a benchmark example from QFT TOOLBOX is considered in this paper, the specifications are readily available in frequency domain.

#### VI.PLANT TEMPLATES

Templates are plot of magnitude verses phase of plant sets for various frequencies. Generation of templates at specified frequencies that pictorially describe region of plant parameter uncertainty on the Nichols chart defines the structured plant parameter uncertainty. The frequency array for plotting the templates must be chosen based on the performance bandwidth and shape of the templates. Margin bounds should be computed up to the frequency where the shape of the plant template becomes invariant to frequency. [5] Here, at approximately  $\omega = 100$  rad/sec, the template's shape becomes fixed, a vertical line. Our array includes several frequencies from  $\omega = 0.1 \text{ rad/sec}$  to  $\omega = 100 \text{ rad/sec}$ .

Fig. 3 Plant Templates

#### VII. STABLITY BOUNDS

It is well known that magnitude of T ( $j\omega$ )  $\leq$  ML establishes a circle in the Nichols Chart. The specifications on system performance in the time domain and in the frequency domain identify a minimum Damping ratio for the dominant roots of the closed-loop system which corresponds to a bound on the value of Mp = Mm. On the NC this bound on Mp = ML establishes a

region which must not be penetrated by the templates and the loop transmission functions for all frequencies. The boundary of this region is referred to as the universal high-frequency boundary (UHFB) or stability bound, the U-contour.

Fig. 4 Stability bounds

#### IX.TRACKING BOUNDS

Depending upon the functions based on upper and lower limit curves, tracking Bounds are generated at various frequencies and different plant sets. Tracking bounds are generated by using MATLAB QFT TOOLBOX command.

Fig. 5 Tracking Bounds

#### X.OUTPUT REJECTION DISTURBANCE BOUND

Depending upon output disturbance rejection transfer function given in the specifications, output disturbance bounds

are generated at various frequencies and for different plants. Disturbance-bounds are generated by using Matlab QFT toolbox command.

Fig. 6 Disturbance Rejection Bounds

#### VIII.GROUOING OF BOUNDS

All the bounds i.e. stability, Tracking and disturbance bounds are grouped together in order to calculate the worst case possibilities. The dominant ones of all the three are retained. Grouped bounds are generated by using Matlab QFT toolbox command. For each frequency there is a dominant bound and is shown in intersection bound window of Matlab.

Fig. 7 Group Bounds

Fig. 8 Dominant Bounds

In this way specifications of closed loop systems for all the plants specified are translated in to that of open loop nominal case.

#### XI.LOOP SHAPING

Loop shaping is a design method where it is attempted to choose a controller such that the loop transfer function obtains the desired shape. It is a key design step and it consists of shaping of the open loop function to set the boundaries given by the design specifications. Manual loop shaping can be done with use of QFT Matlab toolbox. The controller design is undertaken on the NC considering the frequency constraints and the nominal loop L0(s) of the system. At this point, the designer begins to introduce controller functions G(s) and tune their parameters, a process called Loop Shaping, until the best possible controller is reached without violation of the frequency constraints the loop shaping with nominal plant is as shown in figure.

In this paper an initial controller is considered which is given by  $G(s) = \begin{bmatrix} 20s^2 + 12s + 1 \\ s \end{bmatrix}$ . Although the controller is easy to implement; it does not satisfy all the bounds of the QFT

as shown in the fig. In order to obtain the best Controller, Manual loop shaping has to be performed with the help of CAD environment of QFT toolbox in Matlab.

#### XIII.FILTER DESIGN

Once the best controller is designed by manual loop shaping process a pre-filter can be easily designed in order to desired tracking performance specifications, using Matlab QFT toolbox pre-filter is designed.

# XIV.PROBLEMS ASSOCIATED WITH THE MANUAL LOOP SHAPING OF QFT CONTROLLER

The main advantage of QFT controller is that the design Experiences can be used and the design procedure is transparent to the designer. The designer can consider many factors which might be difficult to represent by analytical expressions or quantitatively. However when the plant has unstable zeros or poles or complicated characteristics it may be difficult to design a stabilizing controller manually. In addition, whether or not the design is successful mainly depends on designer's experience applied to trials. Even if manual design is done narrowly, the results are not always satisfying. Also manually designed results are not unique. Usually there are several controllers satisfying with boundary constraints. How to select the best controller from the candidates, i.e., how to realize the optimization of QFT controller, is worthy of investigation. Thus it is necessary to study more automatic QFT controllers. Loop shaping may be considered as the most crucial step of designing a QFT controller. Thus only this particular step is considered in this paper.

## XII.PROPOSED TECHNIQUE FOR TUNING OF QFT CONTROLLER

Compared with above traditional QFT automatic design methods, the GA based loop-shaping technique has many advantages. GA is the most efficient optimization method and can implement multi objective optimization. The controller can be automatically designed by using the computer searching program based on GA to make loop- shaping instead of using manual adjustment. We improve the technique of GA based automatic QFT, and introduce new optimization indexes to make the controller more practical. Compared with results of the manual design and other automatic design methods, the performance of the OFT controller designed by GA is better. The problem that the designer must have experience for loop-shaping is overcome and the problem that it is not easy to design controllers for complex plants is also solved. Although the GA based automatic design method has many advantages mentioned above, many designers who have certain experiences also want to get the best controller in a short time. This is the optimization of OFT controller. What is called optimization of OFT controller is that based on an initial OFT controller, the parameters of the controller are optimized and the performance of the controller is improved. While the automatic design of QFT controller does not have reference information and the parameters region for searching is big. Compared with the automatic design, the searching region is optimal design is much smaller.

#### XV.GENETIC ALGORITHM

Genetic Algorithms (GA's) are a stochastic global search method that mimics the process of natural evolution. The genetic algorithm starts with no knowledge of the correct solution and depends entirely on responses from its environment and evolution operators (i.e. reproduction, crossover and mutation) to arrive at the best solution. By starting at several independent points and searching in parallel, the algorithm

avoids local minima and converging to sub optimal solutions. In this way, GAs have been shown to be capable of locating high performance areas in complex domains without experiencing the difficulties associated with high dimensionality, as may occur with gradient decent techniques or methods that rely on derivative information. A genetic algorithm is typically initialised with a random population consisting of between 20-100 individuals. This population (mating pool) is usually represented by a real- valued number or a binary string called a chromosome. For illustrative purposes, the rest of this section represents each chromosome as a binary string. How well an individual performs a task is measured is assessed by the objective function. The objective function assigns each individual a corresponding number called its fitness. The fitness of each chromosome is assessed and a survival of the fittest strategy is applied. In this project, the magnitude of the error will be used to assess the fitness of each chromosome. There are three main stages of a genetic algorithm; these are known as Reproduction, Crossover and Mutation.

#### **XVI.REPRODUCTION**

During the reproduction phase the fitness value of each chromosome is assessed. This value is used in the selection process to provide bias towards fitter individuals. Just like in natural evolution, a fit chromosome has a higher probability of being selected for reproduction.

Four common methods for selection are:

- 1. Roulette Wheel selection

- 2. Stochastic Universal sampling

- 3. Normalised geometric selection

- 4. Tournament selection

#### XVII.CROSSOVER

Once the selection process is complete, the crossover algorithm is initiated. The crossover operation swaps certain

parts of the two selected strings in a bid to capture the good parts of old chromosomes and create better new ones. Genetic operators manipulate the characters of a chromosome directly, using the assumption that certain individual's gene codes, on average, produce fitter individuals. Following are the three crossover techniques:

- 1. Single-Point Crossover.

- 2. Multi-Point Crossover.

- 3. Uniform Crossover.

#### XVIII.MUTATION

Using selection and crossover on their own will generate a large amount of different strings. However there are two main problems with this:

- 1. Depending on the initial population chosen, there may not be enough diversity in the initial strings to ensure the GA searches the entire problem space.

- 2. The GA may converge on sub-optimum strings due to a bad choice of initial population.

These problems may be overcome by the introduction of a mutation operator into the GA. Mutation is the occasional random alteration of a value of a string position. It is considered a background operator in the genetic algorithm. The probability of mutation is normally low because a high mutation rate would destroy fit strings and degenerate the genetic algorithm into a random search. Mutation probability values of around 0.1% or 0.01% are common, these values represent the probability that a certain string will be selected for mutation i.e. for a probability of 0.1%; one string in one thousand will be selected for mutation.

#### XIX.ELITISM

With crossover and mutation taking place, there is a high risk that the optimum solution could be lost as there is no guarantee that these operators will preserve the fittest string. To counteract this, elitist models are often used. In an elitist model, the best individual from a population is saved before any of these operations take place. After the new population is formed and evaluated, it is examined to see if this best structure has been preserved. If not, the saved copy is reinserted back into the population. The GA then continues on as normal.

The steps involved in creating and implementing a genetic algorithm are as follows:

- 1. Generate an initial, random population of individuals for a fixed size.

- 2. Evaluate their fitness.

- 3. Select the fittest members of the population.

- 4. Reproduce using a probabilistic method (e.g., roulette wheel).

- 5. Implement crossover operation on the reproduced chromosomes (Choosing probabilistically both the crossover site and the 'mates').

- 6. Execute mutation operation with low probability.

- 7. Repeat step 2 until a predefined convergence criterion is met.

#### XX.TERMINATION

This generational process is repeated until a termination condition has been reached. Common terminating conditions are:

- 1. A solution is found that satisfies minimum criteria.

- 2. Fixed number of generations reached.

- 3. Allocated budget (computation time/money) reached.

- 4. The highest ranking solution's fitness is reaching or has Reached a plateau such that successive iterations no Longer produce better results.

- 5. Manual inspection.

- 6. Combinations of the above.

#### XXI.USING THE OPTIMIZATION TOOL

To open the Optimization Tool, enter Optimtool ('ga') at the command line, or enter optimtool and then choose ga from the Solver menu.

To use the Optimization Tool, you must first enter the following information:

#### XXII.FITNESS FUNCTION

The objective function you want to minimize. Enter the fitness function in the form @fitnessfun, where fitnessfun.m is a file that computes the fitness function. The @ sign creates a function handle to fitnessfun. Writing an objective function is the most difficult part of creating a genetic algorithm. In this paper, the objective function is required to evaluate the best PID controller for the DC Motor. An objective function could be created to find a PID controller that gives the smallest overshoot, fastest rise time or quickest settling time but in order to combine all of these objectives it was decided to design an objective function that will minimise the error of the controlled system. Each chromosome in the population is passed into the objective function one at a time. The chromosome is then evaluated and assigned a number to represent its fitness, the bigger its number the better its fitness. The genetic algorithm uses the chromosome's fitness value to create a new population consisting of the fittest members.

In this paper the objective function is defined by various Error Performance Criterion such as MSE, ITAE, ISE, and IAE. The controlled system is given a step input and the error is assessed using an appropriate error performance criterion i.e. ITAE, ISE, IAE or MSE. The chromosome is assigned an overall fitness value according to the magnitude of the error, the smaller the error the larger the fitness value. The above mentioned objective functions are specified with the help of a code in a Matlab file and it is then called appropriately from the objective functions pane.

#### XXIII.NUMBER OF VARIABLES

The length of the input vector to the fitness function is defined by number of variables. In this paper the number of variables are 3 i.e. Kp, Z1, Z2.

# XXIV.CONVERSION OF OFT BOUNDS INTO QUADRATIC INEQUALITIES OR GA CONSTRAINTS

can enter constraints nonlinear constraint function for the problem in the Constraints pane. If the problem is unconstrained, leave these fields blank.

(1) Stability bound given by

$$F \frac{PGH}{1 + PGH} \leq Ws1$$

is converted to a quadratic inequality given by

$$P^{\frac{1}{2}}\left(1-\frac{1}{\delta_1^2}\right)g^{\frac{1}{2}}+2P \exp\left(\xi+\theta^{\frac{1}{2}}g+1\geq t\right)$$

$$p_{e_{*}}^{2} p_{d} (1-1/\delta_{5}^{2})g + 2 p_{e} p_{d} (p_{e} \cos{(Q+f_{d})} - p_{d}/\delta_{5}^{2} \cos{(Q+f_{e})})g + (p_{e}^{2} - p_{d}^{2}/\delta_{5}^{2}) \ge 0$$

Disturbance bound given by

$$F = \frac{H}{1 + PGH} \le WS2$$

is converted to a quadratic inequality given by

$$P^2g^2 + 2 F \cos(\mathcal{C} + \theta) A + \left(1 - \frac{1}{\delta_2^2}\right) \ge 0$$

(3) Tracking bound given by

$$Wsa < F \frac{PG}{1 + PGH} \le Wsd$$

Is converted to a quadratic inequality by

The above derived constraints are specified with the help of a code in a Matlab file and it is then called appropriately from the constraints pane.

Fig. 10 GA Solver window in Matlab

To run the genetic algorithm, click the Start button. The tool displays the results of the optimization in the Run solver and view results pane.

Fig. 11 GA Solver displaying results

The shaped response of control system is shown below:

Fig. 12 Shaped Response of Control System

The above control system can be verified by applying a step input to it and then observing its output response. The response so obtained is very close to step input. So GA based parameter optimization method for QFT controller can accurately adjust parameters on the basis of the results from manual design method, which can obtain good QFT controller in a short time. Thus it is good combination of manual and automatic design.

Fig. 13 Step Response Of Control System verifying the results in the paper

#### **CONCLUSION**

QFT can provide robust control for the plant with large uncertainties. But for the complicated plant, it is hard to get the controller by manual design with the help of QFT toolbox in Matlab. Traditional automatic design has limited capability with such multiple objective optimization problems as what appears in

QFT CONTROLLER design. But GA is a more efficacious global optimization method; it can make optimization aiming to multiple goals. So in this paper, we present the automatic design method of QFT controller based on GA, and propose several optimization indices to make controller more practical. Then the paper expatiates on optimal design methods which combines the manual design and automatic design. The experiment shows that the GA based automatic design method of QFT controller is very effective and optimal design method can achieve both high performance and increased searching efficiency.

#### REFERENCES

- [1] I. J. Nagrath and M. Gopal, Control Systems Engineering, New Age International (P) Limited.

- [2] R C. Dorf, Modern Control Systems, Addison-Wesley Publishing Company, 5th edition, 1990.

- [3] Houpis, C.H., S. J. Rasmussen and M. Garcia-Sanz, Quantitative Feedback Theory - Fundamentals and Applications, 2nd Edition, Taylor & Francis, 2006.

- B. C. Kuo, Automatic Control Systems, Prentice-Hall International Editions, 1991.

- Borghesani, C., Y. Chait, O. Yaniv, Quantitative Feedback Theory Toolbox v2.0 - For use with MATLAB, Terasoft, 2003.

- [6] Chen, W., D.J. Balance and Y. Li, "Automatic loop-shaping in QFT using genetic algorithms," Proceedings of the 3rd Asia-Pacific Conference on Control and Measurement, pp. 63-67,

- [7] Qingwei Wang, Zhenghua Liu, Lianjie Er, School of Automation Science and Electrical Engineering, Beijing University of Aeronautics and Astronautics. Beijing 100083.

- BRYANT G.F. and HALIKIAS G.D., 1995, Optimal loop shaping for systems with large parameter uncertainty via linear programming. International Journal of Control, 62, 557-

- Horowitz, I. M., "Survey of quantitative feedback theory (QFT)", International Journal of Control, 53 (2), 1991, pp. 255-291.

- [10] Chait Y and Yaniv O. (1993), Multi-input/single-output computer-aided control design using the Quantitative Feedback Theory. Int. J. Robust Nonlinear Control, 1993, No.3, pp. 47-54.

- [11] Mario Garcia-Sanz, Automatic Control and Computer Science Department, Public University of Navarra. Campus, Arrosadia, 31006, Pamplona, Spain.

- [12] Horowitz I.M., "Optimum loop transfer function in single-loop minimum-phase feedback systems," Int. J. Control, vol. 18, no. 1, pp. 97-113, 1973.

[13] Ibtissem Chiha, 1 Noureddine Liouane, 2 and Pierre Borne3, Tuning PID Controller Using Multi-objective Ant Colony Optimization.

# DATA ACQUISITION THROUGH GSM

Prof.Meera .B. Kharat Department of Electronics Engineering PIIT. New Panvel

Ankur Upadhyay Department of Electronics Engineering PIIT, New Panvel

ankupadhyay@gmail.com

meerakharat13@gmail.com

Abstract—The purpose of this device is used for acquiring data from remote location using PC .The data to be acquired is collected by micro controller that is installed at industrial location and is connected to various machines. The micro controller continuously records whatever parameters it is programmed to record and display them on display screen. The micro controller is also connected to mobile. A PC installed in an office at a distance location can connect to this micro controller to mobile. Whenever the data is to be acquired the PC dials up the number of micro controller line. Once the connection is made PC sends the command to the micro controller giving the details of required. The micro controller then sends the demanded data to the PC .the data acquired by the micro controller is in digital format and is stored in EEPROM .The PC automatically generates the file name and stores data along with the real time.

#### 1. INTRODUCTION

Data acquisition systems have evolved rapidly in the past few decades fueled by the advances in electrical computer engineering and computer science. Standardized input output interfaces have allowed for the development of peripherals such as transducers that connect seamlessly to the computer and make the task of data acquisition a simple one. Data acquisition systems have become faster and relatively inexpensive [2]. They have also experienced a reduction in size and are more reliable. Their high accuracy has made them

an essential tool in a wide range of research areas where quantitative methods of analysis are required. DAS plays important role in engineering experiments. Data acquisition system is the process by which events in the real world are sampled and translated into machine- readable signals [1]. Sometimes abbreviated DAQ data acquisition typically involves sensors, transmitters and other instruments to collect signals, waveforms etc. to be processed and with a computer. A typical data acquisition system in common use is the data acquisition card, which can be inserted in the PC main board and make a PC- based data acquisition system. The first step in data acquisition is to detect and convert physical characteristics, such as pressure, temperature, and flow rate, and position into an electrical signal. This is done using a transducer is a

Device that converts a physical quantity into an electrical signal. Transducers have several important properties. One such property is linearity. Data acquisition systems, as the name implies, are products and/or processes used to collect information to document or analyze some phenomenon. In the simplest form, a technician logging the temperature of an oven on a piece of paper is performing data acquisition. As technology has progressed, this type of process has been simplified and made more accurate, versatile, and reliable through electronic equipment. Equipment ranges from simple recorders to sophisticated computer systems [1] [3]. Data acquisition products serve as a focal point in a system, tying together a wide variety of products, such as sensors that indicate temperature, flow, level, or pressure.

#### II. METHODOLOGY

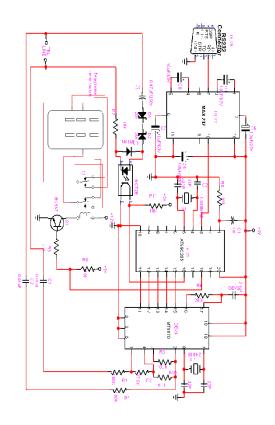

#### A. Hardware Description

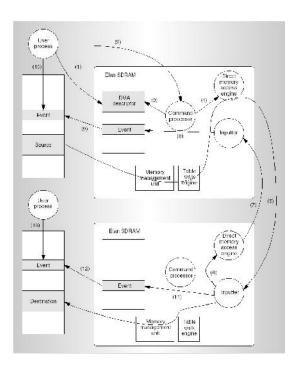

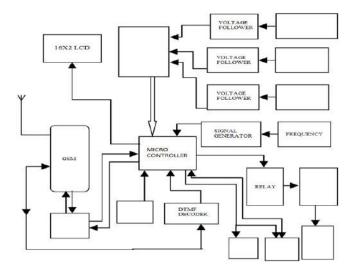

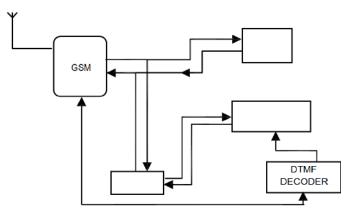

This system is used to access data from remote location Using PC the data is to acquire is collected by microcontroller and it is stored in EEPROM. The data which is stored in EEPROM is continuously displayed on LCD display. In this system data acquisition is done by GSM module .When the person wants to access the data from receiver side one can directly dial the mobile number present at transmitter side. Once the number dialed and connection is established microcontroller will get the signal from DTMF decoder that call is arrived. Then the microcontroller will send the signal SOC to ADC and after reading the complete data from ADC it will send the signal EOC to microcontroller. The microcontroller then sends the recorded data to PC through GSM module. PC is interfaced with GSM module through RS232 port. The same data which is recorded at transmitter can be seen at receiver on PC. The data can be taken at regular interval. The data which is to be taken are different parameters like temperature, voltage, current and frequency. For temperature sensor is used in the system which will record the present temperature. For current, current transformer is used which is applied channel-2 of ADC. For voltage, voltage transformer is used which is applied channel-1 of ADC. Frequency input is taken from NAND gate here two NAND gates are shorted which will act as signal conditioning and then applied to microcontroller. In this system these four parameters are recorded at transmitter and these data can be accessed at receiver by simply dialing the number of transmitter. Data transmission is done through GSM module. It's a wireless communication system. RTC is also used in this project so that it will display the time as well when the data is recorded. Thus the system is use to acquire data from remote location the data acquire in the system is through GSM.

Block Diagram of Data Acquisition through GSM (Transmitter)

#### B. System Model

This device is used for acquiring data from a remote location using a PC[1]. The readings which are supposed to be recorded are temperature, current and frequency. For temperature sensor LM34 IC is used in the system which will record the present temperature it is applied to voltage follower and then to channel-0 of ADC For current, current transformer is used which is applied to voltage follower and then to channel-2 of ADC. For voltage, voltage transformer is used which is applied to voltage follower and to Channel-1 of ADC. The output of all these parameters is applied to voltage follower so that no leakage in voltage takes place. Frequency input is taken from NAND gate here two NAND gates are shorted which will act as signal conditioning and then applied to microcontroller,

These parameters are continuously recorded in microcontroller and stored in EEPROM .It is volatile memory. Even if supply is not there data will remain in it. At the same time the data is displayed on LCD display. Whenever the device present at remote location wants to acquire the data it will directly dial GSM number of transmitter. The GSM module at transmitter is interfaced with microcontroller with RS232 serial bus. The call is decoded at microcontroller with help of DTMF decoder, as shown in figure then the

microcontroller sends SOC signal to ADC Then the ADC will convert all these signals to digital and are applied to microcontroller. After sending all the data to microcontroller ADC will send EOC pulse to microcontroller, then microcontroller sends SOC signal to ADC Then the ADC will convert all these signals to digital and are applied to microcontroller. After sending all the data to microcontroller ADC will send EOC pulse to microcontroller.

After getting all the data it is send to receiver through GSM module. Data communication is done through GSM. When all the data comes at receiver side through DTMF decoder, it will decode the pulses and are applied to microcontroller. The microcontroller, GSM and PC are interfaced with RS232 serial The transmitter of RS232 is connected to receiver of microcontroller and receiver of RS232 is connected to transmitter of microcontroller. Thus same data which is recorded at transmitter can be seen at receiver on PC. The data can be taken at regular interval, Keys which are present at transmitter are push to on and are normally use to set the parameter readings as per the requirement. If the system crosses the set value then it will automatically switch off the load. Relays which are used in the system are use to drive the load if the system is over loaded. RTC is also used at transmitter so that whatever parameter is recorded it will record the time as well. Once the data is read on PC it can Again dial the GSM number for next slot of data, thus the data can be recorded at regular interval is clear by figure

#### C. Compiling the code